Note: There may be a lot of errors at this point in the Messages pane. Rename the newly added JTAG UART component to jtag_uart.Do not change anything and click Finish.Back in the Library pane, expand Interface Protocols, expand Serial, and add JTAG UART.We need a JTAG UART to program and communicate with the FPGA. Hit Ctrl-R to rename the processor to cpu. Back in the System Contents tab, select nios2_qsys_0.Do not change anything else and click Finish. In the next window, select Nios II/e under "Select a Nios II Core".Expand Embedded Processors, select Nios II Processor, and click the Add button at the bottom of the pane. First find the Library pane on the left side of the page.After Qsys is opened, save the file as Lab12LCD.qsys.Now let's add the Nios II processor that will control the LCD. Click on the Tools menu and click on Qsys.

This will open Quartus with the Lab 12 project files. Navigate to Documents\Lab12 and double-click on Lab12.QPF.Now let's generate the hardware descriptions of the LCD panel and controller, which will be the Nios II CPU. When you are done, click Generate and save the files in Documents\Lab12.In the System Builder, deselect all components but CLOCK and LCD.It is normally located in C:\FPGA-Lab\DE2-115\DE2_115_SystemBuilder_V201\DE2_115_SystemBuilder.exe. It has since been updated to work with Quartus v13.1.įirst, we must create the necessary Quartus files for this lab. Note: This lab was originally created for Quartus v9.1.

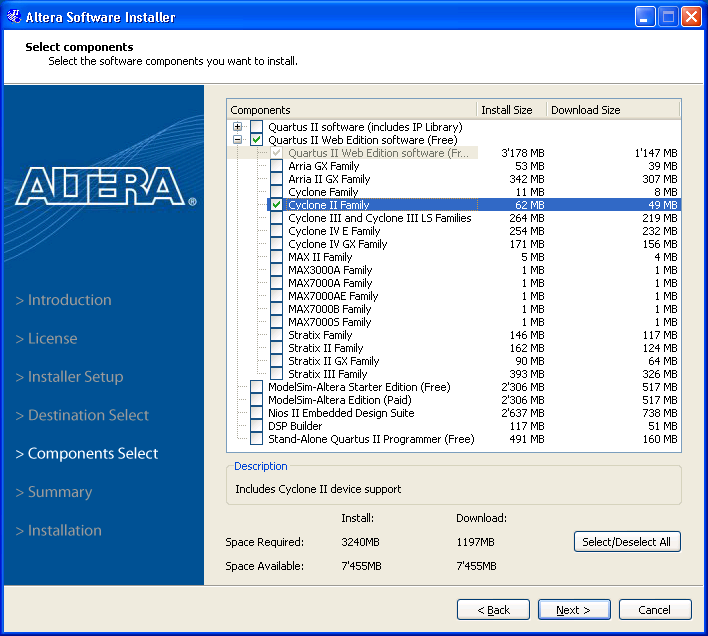

#ALTERA QUARTUS II V9.0 HOW TO#

The purpose of this tutorial is to teach users how to write text to the LCD of the Terasic DE2-115 FPGA development kit. "Hello world" on the Terasic DE2-115 LCD Component

0 kommentar(er)

0 kommentar(er)